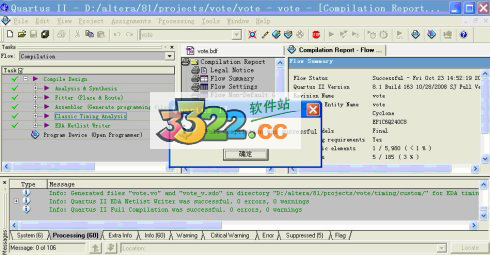

quartus ii 11.0是用于SOPC的FPGA设计软件,其因为强大的设计能力和直观易用的接口而深受数字系统设计者的欢迎。它提供最为完善的timing closure和LogicLock基于块的设计流程,同时它也是唯一一个包括timing closure和基于块的设计流为基本特征的PLD软件。quartus ii 11.0是目前唯一提供FPGA和固定功能HardCopy器件统一设计流程的设计工具,用户可以利用这个工具对Stratix FPGA进行功能验证和原型设计,且可设计HardCopy Stratix器件用于批量成品。新版quartus ii 11.0改进了性能、提升了功能性、解决了潜在的设计延迟等旧版存在的问题,并且在工业领域率先提供FPGA与mask-programmed devices开发的统一工作流程。

一、点击安装文件夹,并双击“11.0_quartus_windows.exe”

二、进行文件夹的解压,默认的解压路径为C:UsersADMINI~1AppDataLocalTemp,或点击Browse可更换解压路径,完成路径选择并点击“Install”

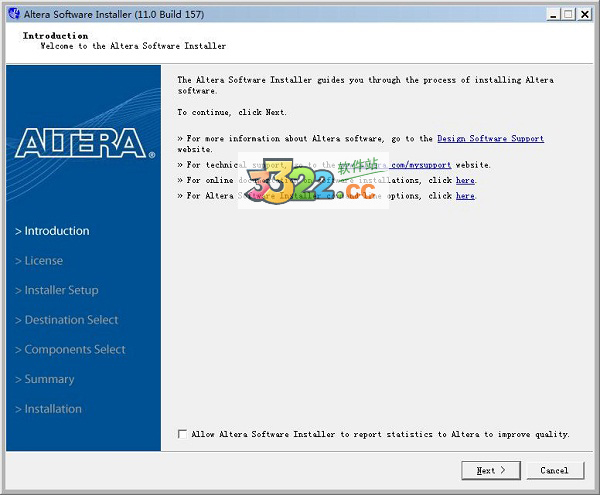

三、提示用户正在安装quartus ii 11.0破解版,无需过多浏览什么直接点击“Next”

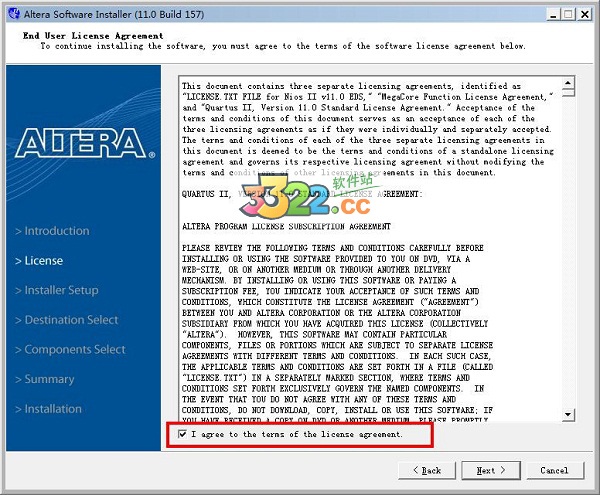

四、浏览相关的安装协议,并勾选“I agree to the terms of the....”即同意此协议,勾选完成,点击“Next”

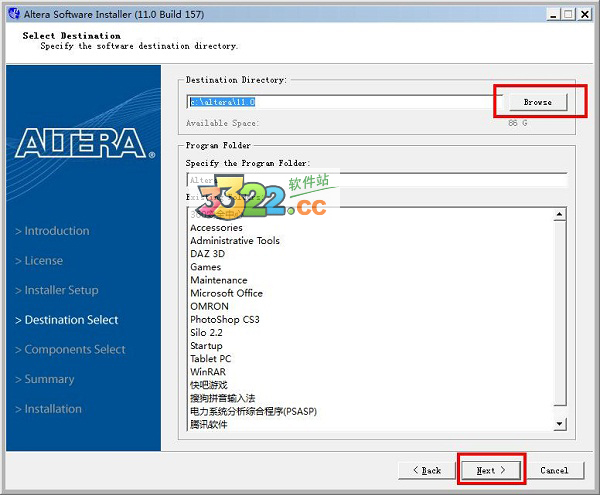

五、选择软件的安装路径,默认路径为c:altera11.0,若需要更改路径可点击browse更换安装路径,并可设置软件的所在文件夹的文件名建议默认,完成设置点击Next

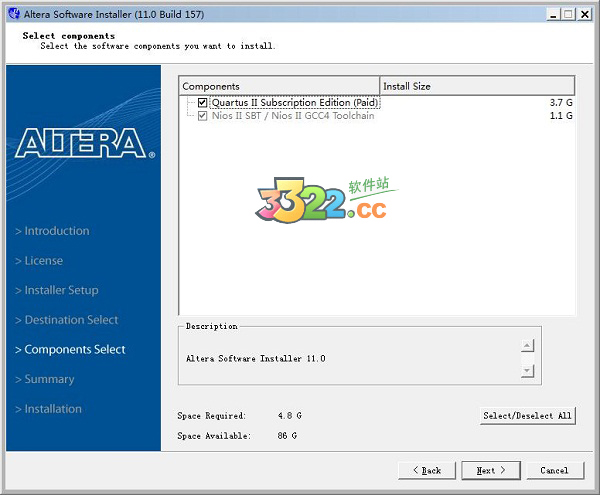

六、选择安装组件,默认勾选:

1.Quartus II Subscription Edition

2.NIos II SBT/NIos II GCC4 TOOLchain

建议全部勾选,但需要注意安装这些程序需要4.8G的空间,若所在硬盘空间不够,可点击Back返回修改安装路径,完成点击Next开始正式的安装

七、开始正式的安装,安装的时间可能过长,用户需耐心等待,之后点击finish完成安装并退出

一、

解压缩

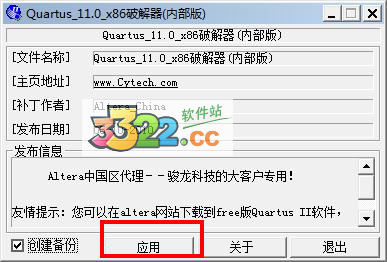

后,复制解压出来的文件“Quartus_11.0_x86破解器(内部版).exe”到Quartus软件安装的目录下

二、双击打开破解文件,直接点击“应用”按纽

三、然后选中sys_cpt.dll,点击“打开”安装默认的sys_cpt.dll路径是在C:altera11.0quartusbin下)

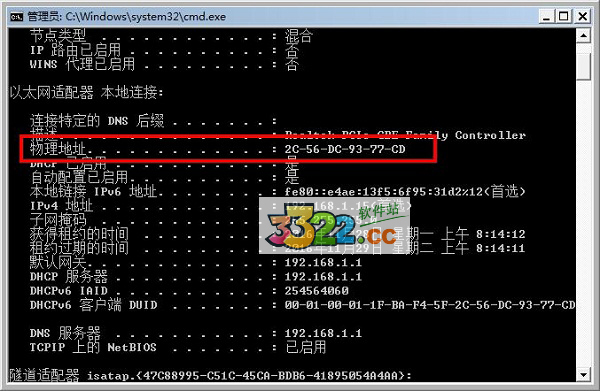

四、把license.dat里的XXXXXXXXXXXX用自己的网卡号替换,网卡号查询方法:

方法一

在Quartus的Tools菜单下选择License Setup,下面就有NIC ID

方法二

打开命令提示符(开始---运行==输入cmd)界面输入,ipconfig /all 可以看到网卡的物理地址

方法三

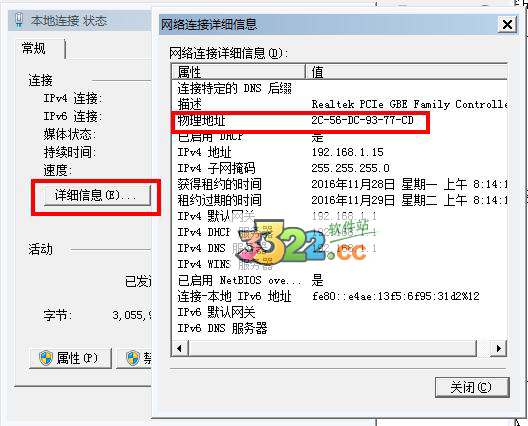

1.打开

任务栏

右下角----找到 “打开网络和共享中心”

2.出现的网络和共享中心菜单中,找到“更改适配器设置”

3.然后就能看到当前系统的网卡设备了,找到需要查看的网卡设备如“本地连接”选择“状态”可以查看网卡详细信息

五、在Quartus II 11.0的Tools菜单下选择License Setup,然后选择License file,最后点击OK

六、完成破解,用户可完全免费使用quartus ii 11.0破解版啦

一、套件

用户要想完整的使用 ,需要安装相应的套件,需下载的套件:

1.Quartus II 9.1之前的软件自带仿真组件,而之后软件不再包含此组件,因此必须要仿真安装Modelsim

2.Quartus II 9.1之前的软件自带硬件库,不需要额外下载安装,而10.0开始需要额外下载硬件库,另行选择安装

3.Quartus II 11.0之前的软件需要额外下载Nios II 组件若需要上系统,而11.0开始Quartus II 软件自带Nios II组件

4.Quartus II 9.1之前的软件自带SOPC组件,而Quartus 10.0自带SOPC已经Qsys两个组件,但从10.1开始,Quartus II之包含Qsys组件

5.Quartus II 10.1之前软件包括时钟综合器,即Settings中包含TimeQuest Timing Analyzer,以及Classic Timing Analyzer,但10.1以后的版本只包含了TimeQuset Time Analyzer,因此需要sdc来约束时序

二、组件

1.11.0_quartus_windows.exe :Quartus II 软件

2.11.0_devices_windows.exe :Quartus II 硬件库

3. 11.0_modelsim_ase_windows.exe :Altera Modelsim 仿真软件

一、QuartusII中的优化设置

一般都会在assignment/settings中进行设置

1.全局优化

在assignment/settings/,physical synthesis optimization中,有几个选项:

(1)optimize for performance(性能优化)

perform physical synthesis for combinational logic 对组合逻辑进行优化

perform register retiming 对寄存器进行优化

(2)effort level 级别

相应的不同的级别的不同之处在后面的解释中说明,主要体现在了编译时间的多少,当然与提高的性能之间呈反比的关系

(3)fitter netlist optimization 布局布线网表优化

第一个选项是对异步信号自动的添加流水线

第二个选项执行寄存器的复用

(4)optimize for fitting 布局布线的优化

第一个选项是针对组合逻辑电路而言

第二个选项 对逻辑和寄存器进行优化

2.综合优化

在优化技巧(optimization technique)中有三种选择:即: 速度优先,平衡优先,面积优先,还有powerplay power optimization即功率优化

若选择extra effort,综合器将进行功率优化,但可能会降低整个设计的性能

3.适配优化

包括保持时序优化 多拐角时序优化

保持时序优化允许适配器通过在合适的路径中添加延迟,从而实现保持时序的优化,关闭该选项,则不会对任何路径进行优化

多拐角时序优化用于控制适配器是否对设计进行优化以满足所有拐角的时序要求和操作条件。要使用这项功能,必须使能时序逻辑优化

1、支持MAX7000/MAX3000等乘积项器件

quartus ii 11.0设计软件现在除了支持Altera的APEX 20KE,APEX 20KC, APEX II,ARM的Excalibur嵌入处理器方案,Mercury,FLEX10KE和ACEX1K之外,还支持MAX3000A,MAX7000系列乘积项器件。MAX3000A和MAX7000设计者现在可 以使用QuartusII设计软件中才有的所有强大的功能

2、软件体积缩小,运行速度加快

安装软件为290M,完全安装为700M,如果定制安装,不选择Excalibur嵌入处理器,则安装所需空间为 460M,比QuartusII1.1版本减少一半以上的空间要求,却能支持ALTERA全部芯片的开发。同时软件的装载,编译,仿真速度比1.1版本大 大加快

3、LogicLock设计流程把性能提升15%

quartus ii 11.0设计软件通过增强层次LogicLock模块级设计方式,将性能平均改善15%。 LogicLock设计流程把整个模块的放置交由设计者控制,如果必要的话,可以采用辅助平面布置。LogicLock设计流程运行设计者单独地优化和锁定每个模块的性能,在大型SOPC设计的构建过程中也保持整个系统的性能。2.0版Quartus II设计软件把新的LogicLock设计流程算法集成到未来的Altera器 件中,该算法充分利用了模块级设计的优势

4、采用快速适配选项缩短编译时间

增加了一个新的快速适配编译选项,选择中这个选项,将会比缺省设置要缩短50%的编译时间。快速适配功能保留了 最佳性能的设置,加快了编译过程。这样布局适配算法反复的次数更少,编译速度更快,对设计性能的影响最小

5、新的功能减小了系统级验证

设计软件引入了新的功能,加快验证过程,这通常是SOPC设计流程中最漫长的阶段。在最初的编译时间中,新的SignalProbe技术允许用 户在保留设计最初布线,时限和设计文件的同时把内部节点引到未用的管脚进行分析。SignalProbe技术完成了现有SignalTap嵌入逻辑分析的功能。 而且设计者能够使用新版本中提供的HDL测试模板快速地开发HDL仿真矢量

1、DSP Builder 12.0新的数字信号处理(DSP)支持——通过系统控制台,与MATLAB的DDR存储器进行通信,并具有新的浮点功能,提高了设计效能,以及DSP效率

2、经过改进的视频和

图像处理

(VIP)套装以及视频接口IP——通过具有边缘自适应算法的Scaler II MegaCore功能以及新的Avalon-Streaming (Avalon-ST)视频监视和跟踪系统IP内核,简化了视频处理应用的开发

3、增强收发器设计和验证—更新了Arria V FPGA的收发器工具包支持,进一步提高收发器数据速率(对于Stratix V FPGA,高达14.1 Gbps)

1、Quartus II设计软件也可以自动地从QuartusII仿真器波形文件中创建完整的HDL测试平台

2、支持高速I/O设计,生成专用I/O缓冲信息规范(IBIS)模型导入到常用的EDA信号集成工具中。IBIS模型根据设计中每个管脚的I/O标准设置来定制,简化第三方工具的分析

3、支持双核CPU的嵌入

4、可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;

芯片(电路)平面布局连线编辑

5、LogicLock增量设计方法,用户可建立并优化系统,然后添加对原始系统的性能影响较小或无影响的后续模块

功能强大的逻辑综合工具

6、完备的电路功能仿真与时序逻辑仿真工具

7、定时/时序分析与关键路径延时分析

8、可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析

9、支持软件源文件的添加和创建,并将它们链接起来生成编程文件

10、使用组合编译方式可一次完成整体设计流程

11、自动定位编译错误

12、高效的期间编程与验证工具

13、可读入标准的EDIF网表文件、VHDL网表文件和Verilog网表文件

14、能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件

1、具体问题

安装quartus ii 11.0软件后,经过破解器生成license.dat文件后,实际建立工程后,编译综合工程的时候会出现license.dat文件与芯片不匹配的问题

2、细节描述

Warning: FLEXlm software error: Invalid (inconsistent) license key. The license key and data for the feature do not match. This usually happens when a license file has been altered. Feature: quartus License path: C:alteralicense.dat; FLEXnet Licensing error:-8,523 For further information, refer to the FLEXnet Licensing documentation, available at www.acresso.com

Error: Current license file does not support the EP2C8Q208C8 device

3、解决方案

在运行破解器生成license.dat文件后,用记事本格式打开license.dat文件,将里面host ID后面的XXXXXXXXXXXX改成你电脑的网卡号,注意license.dat文件中存在两个host ID号。其实打开已安装好的

quartus ii 11.0软件后,选择tools->License Setup窗口,可以找到两个NIC ID号,刚好按先后顺序填写入license.dat文件中的两个host ID,就可以了

优诚商贸通

电脑学习

金税三期个人所得税扣缴系统客户端

电脑学习

打扮家bim官方版

电脑学习

中国农业银行网银助手

电脑学习

电销猫电脑版

电脑学习

CAMWorks

电脑学习

TRNSYS中文版

电脑学习

proteus 8.4破解版

电脑学习

Revit2016中文版

电脑学习

小猿搜题电脑版

电脑学习

打字高手一周速成官方

电脑学习

电脑应用一软通官方下载

电脑学习

狼人杀官方正版 v3.0.2.1 安卓版

脑力开发

口袋狼人杀破解版 v3.0.2.1 安卓版

脑力开发

围棋手机版 v1.27 安卓版

脑力开发

棋牌21点手机版 v5.9.0 安卓版

脑力开发

红心大战游戏 v1.0.1 安卓版

脑力开发

江汉游仙桃晃晃完整版 v5.5 安卓版

脑力开发

炉石传说美服手机版 v19.2.69054 安卓版

脑力开发

指上谈兵手游 v2.0.0 安卓版

脑力开发